发布日期:2026-04-26 浏览次数:

导航:X技术最新专利计算;推算;计数设备的制造及其应用技术

本发明针对异构众核系统中线程数设置不合理导致性能与能耗失衡的问题,提出基于硬件性能计数器动态采集数据,利用预测模型实时计算最优线程数的调整方法。通过分析程序运行状态与硬件特性,动态优化线程分配,实现性能提升与能耗降低的协同优化。

[0001] 本发明属于计算机系统结构领域,涉及一种并行应用程序线程数动态调整方法, 尤其涉及一种用于异构众核系统下的应用程序线程数动态调整方法。

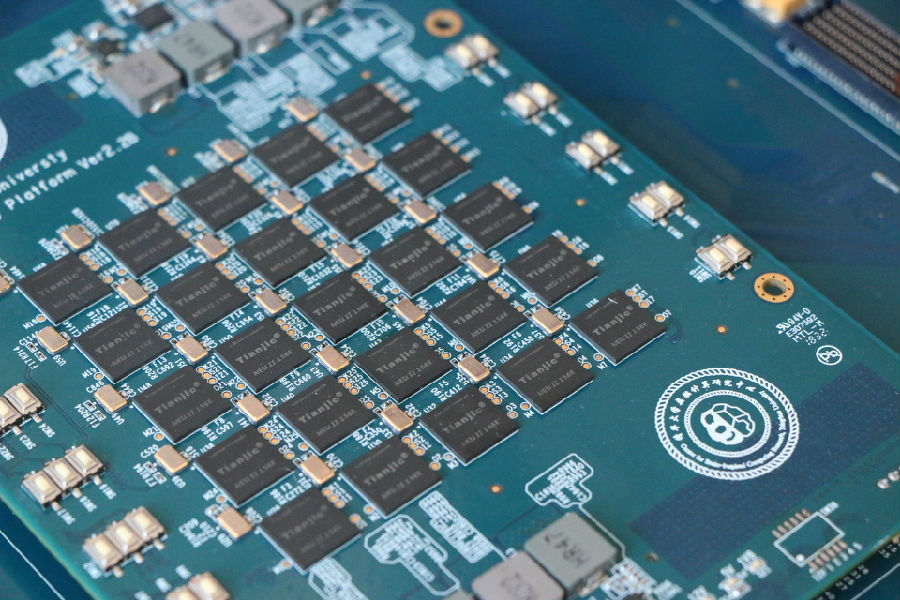

[0002] 随着多核、众核技术的迅速发展,异构系统已经成为高性能计算领域一种重要的 发展趋势,如何在充分利用异构系统高计算能力提升程序性能的同时,降低系统的能耗是 异构系统需要解决的一个关键问题。在主处理器+协处理器架构的新型异构众核系统下, 主处理器主要负责处理复杂的逻辑控制任务,协处理器负责处理计算密度高、逻辑分支简 单的大规模数据并行任务,主处理器和协处理器协同的计算任务的不同部分,为具体的应 用程序提供高效的计算平台。在具体运行程序时,如何在主处理器和协处理器端设置线程 数,对程序性能、异构系统整体能耗都将产生重要的影响。

[0003] 异构PG中国电子技术有限公司众核系统下,主处理器一般采用通用的片上多核处理器(CMP),因处理器核数 有限,通常在CMP上将线程数设置为具体的处理器核数,就能达到较好的加速效果。协处理 器通常采用新型众核处理器(如GPU和MIC),由于处理器核数众多(通常几十、上百个核), 同时处理核内部又引入了同时多线程(SMT)技术,这使得影响因素更加复杂。如果设置的 线程数过多,会因线程间争用共享资源导致计算性能下降,同时由于启用众多的处理核会 造成过高的能源消耗;设置的线程数过少,则因异构系统处理核资源得不到充分利用,影响 计算性能的提升。又因主处理器和协处理器具有不同的硬件架构,如何根据分配到的任务 特点,结合硬件架构特征合理的设置线程数,将任务映射到具体的处理核上,对充分利用不 同处理器的硬件资源、高效发挥异构众核系统的计算能力及提高异构众核系统整体效能具 有重要意义。

[0004] 已有的针对多核及众核环境下,确定多线程应用程序最佳线程数的研宄工作,总 体上可以分为根据经验值静态设置、迭代探测、预测三种实现方法。由于受所处理数据及具 体运行平台的变化等因素影响,根据经验值静态设置的方法通常不能正确的反映程序具体 运行时的特性,准确性和性能较低;迭代探测的方法通过在程序运行过程中不断的测试对 比不同的线程数对性能的影响,最终找到近似最优的线程数,然后以此为标准进行线程映 射,但该方法会引入较高的额外开销,不能反映程序动态变化的特性;预测的方法介于前两 者之间,结合一定的模型,估计出最优的线] 已有的工作主要针对传统的多核及众核环境研宄相应的最优线程数,但在由主处 理器和协处理器构成的异构众核系统下,协处理器集成了更多数量的处理核,主处理器和 协处理器协同的处理计算任务,要根据架构特征,结合应用程序本身的特点及程序在运行 过程中运行状态才能设置合理的线程数,从而保证程序计算性能的同时最大程度的降低系 统能耗,而已有的在传统的多核及众核环境下确定最佳线程数的方法不能较好的适应新型 异构众核系统。

[0006] 由于存在以上问题,目前还没有一种能够根据异构众核系统架构的特征,结合应 用程序在运行过程中阶段性变化的特性,实时对并行应用程序的线程数进行动态调整以较 低的开销在提高程序的计算性能同时降低系统能耗的有效方法。

【发明内容】[0007] 本发明的目的在于克服上述现有技术中的问题,提供一种异构众核系统下的用于 异构众核系统下的应用程序线程数动态调整方法,该线程数动态调整方法以最优线程数动 态预测模型为基础,可以在保证应用程序理想计算性能的同时尽量降低系统的整体能耗。

[0009] 1)异构系PG中国电子技术有限公司统主机端主进程将程序循环部分代码分派到异构系统的协处理器上运 行,通过系统硬件性能记数器获取程序在不同的线程数运行情况下的IPSdP IPSn的值,其 中IPS1为单个线程运行时程序每秒钟所处理的指令数,IPS 为η个线程运行时程序每秒钟 所处理的指令数;

[0010] 2)将收集到的状态信息IPS#不同线程数情况下的IPS遁返回到CPU主机端;

[0011] 3) CPU主机端根据以下公式计算多线程运行时相对于单个线程运行时的相对周转 时间fn:

1. 一种用于异构众核系统下的应用程序线程数动态调整方法,其特征在于,包括如下 步骤:1) 异构系统主机端主进程将程序循环部分代码分派到异构系统的协处理器上运行,通 过系统硬件性能记数器获取程序在不同的线程数运行情况下的IPSdP IPSn的值,其中IPS1为单个线程运行时程序每秒钟所处理的指令数,IPSnS η个线程运行时程序每秒钟所处理 的指令数;2) 将收集到的状态信息IPSJP不同线程数情况下的IPS ^直返回到CPU主机端;3. CPU主机端根据以下公式计算多线程运行时相对于单个线程运行时的相对周转时间fr-

公式(1)中TTdP TT1分别表示多线程运行时程序的执行时间和单线程运行时的程序 执行时间,SIP为程序总的指令数;3) 根据公式(1)计算得到多组(fn,η)值,利用最小二乘法,通过求解以下方程组:

计算出最优线程数预测模型中的系数α,β的值,其中α表示所处理任务中的串行比 例系数、β表示并行任务比例系统、γ表示额外开销对性能的影响因子;4) 根据最优线程数预测模型:

计算最优线)中计算出的α和β的值代入公式(2)计算出最优线程数预测值η,将应 用程序的线程数设为最优线程数η后重新在协处理器端运行应用程序;同时以最优线程数 为标准将空闲的处理核及处理核内部的硬件线程关闭或置于非活动状态;6) 程序在协处理器端运行的过程中,在一定的时间间隔内对程序的运行状态信息采集 一次,并对程序的运行状态进行检测;如果检测到程序发生阶段性变化,则转到步骤2);如 果程序在协处理器端运行过程中没有检测到阶段性变化,则继续运行程序,直到程序运行 结束;7) 将协处理器端的运行结果返回给主机端,主机端继续执行整个应用程序的后继部 分,遇到有循环部分则继续分派到协处理器端执行,即转到步骤1);8) 不断的迭代直到整个应用程序执行完成,从而实现了在应用程序运行的过程中动态 的对线所述的用于异构众核系统下的应用程序线程数动态调整方法,其特 征在于:所述步骤4)中的最优线程数预测模型根据以下多线程运行时相对于单线程运行 时的周转时间计算公式推导后得到: 1) 经过对Amdahl定律扩展变换后得公式(3):

2) 通过利用极值定理求解使公式(4)中相对周转时间最小的值n,即可以得到最优线所述的用于异构众核系统下的应用程序线程数动态调整方法,其特 征在于:所述步骤6)中,对程序的运行状态进行检测是根据采集到的线程上下文切换率、 线程迀移率、cache缺失率、CPU利用率以及带宽利用率这五个指标判断程序的运行状态是 否发生了阶段性的变化。

4. 根据权利要求1基于预测模型的异构众核系统应用程序线程数动态调整方法,其特 征在于:所述步骤6)中的状态信息采样间隔为100ms。

【专利摘要】本发明公开了一种用于异构众核系统下的应用程序线程数动态调整方法,该方法以异构众核硬件架构特征和程序运行时动态阶段性变化的特性为基础,通过采集反映程序性能变化的系统级性能计数器的状态信息,利用预测模型实时估计出最优的线程数,以此为指导动态的对应用程序的线程数进行调整。为保证合理的利用异构众核系统的计算资源来提高程序计算性能的同时降低系统能耗提供了一个有效的解决方法。

【发明人】董小社, 巨涛, 朱正东, 李亮, 白秀秀, 吴树森, 魏晓林

针对异构众核处理器资源占用高、通信复杂、扩展性差的问题,提出基于片上总线和共享内存的异构众核ASIP架构。通过共享内存实现多端口无冲突读写,节约存储资源;采用Wishbone总线统一通信,降低...

针对异构众核体系结构中传统通信模型存在的中断开销大、控制核心热点问题,提出基于扁平化模型的通信实现方法。通过控制核心主动轮询处理运算核心消息请求,实现点对点通信的批量处理;利用单核心通知与阵列...

1.计算机网络安全 2.计算机仿线.网络安全;物联网安全 、大数据安全 2.安全态势感知、舆情分析和控制 3.区块链及应用